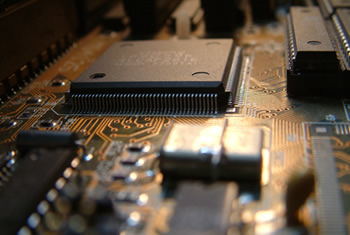

1nm晶体管诞生 目前为止全球最小的晶体管!

晶体管的制程大小一直是计算技术进步的硬指标。晶体管越小,同样体积的芯片上就能集成更多,这样一来处理器的性能和功耗都能会获得巨大进步。

多年以来,技术的发展都在遵循摩尔定律,即当价格不变时,集成电路上可容纳的元器件的数目,约每隔18-24个月便会增加一倍,性能也将提升一倍。换言之,每一美元所能买到的电脑性能,将每隔18-24个月翻一倍以上。眼下,我们使用的主流芯片制程为14nm,而明年,整个业界就将开始向10nm制程发展。

不过放眼未来,摩尔定律开始有些失灵了,因为从芯片的制造来看,7nm就是物理极限。一旦晶体管大小低于这一数字,它们在物理形态上就会非常集中,以至于产生量子隧穿效应,为芯片制造带来巨大**。因此,业界普遍认为,想解决这一问题就必须突破现有的逻辑门电路设计,让电子能持续在各个逻辑门之间穿梭。

此前,英特尔等芯片巨头表示它们将寻找能替代硅的新原料来制作7nm晶体管,现在劳伦斯伯克利国家实验室走在了前面,它们的1nm晶体管由纳米碳管和二硫化钼(MoS2)制作而成。MoS2将担起原本半导体的职责,而纳米碳管则负责控制逻辑门中电子的流向。

眼下,这一研究还停留在初级阶段,毕竟在14nm的制程下,一个模具上就有超过10亿个晶体管,而要将晶体管缩小到1nm,大规模量产的困难有些过于巨大。

不过,这一研究依然具有非常重要的指导意义,新材料的发现未来将大大提升电脑的计算能力。

相关内容

-

公制和英制的区别

公制和英制的区别,,1、计量单位不同:公制单位是以毫米为单位计算尺寸。英制单位是以英寸为单位计算尺寸。2、含义不同:英制:是英国、美国等英语国家使用的一种度量制。长度主单位为英尺,重量主单位为磅,容积主单位为加仑,温度单位为华氏度。因为各种各样的历史原因,英制的进制相当繁杂。公制:亦称“米制”、“米突制”。1858年《中法通商章程》签定后传入中国的一种国际度量衡制度。创始于法国,1795年4月7日...

-

内六角公制和英制的区别

内六角公制和英制的区别,,1、性质不同:公制单位是以毫米为单位计算尺寸的,英制单位是以英寸为单位计算尺寸的。2、特点不同:公制螺纹是60度等边牙型,英制螺纹是等腰55度牙型,美制螺纹60度。3、单位不同:公制螺纹用公制单位, 美英制螺纹用英制单位。 4、用途不同:管螺纹主要用来进行管道的连接,其内外螺纹的配合紧密,有直管与锥管两种。公称直径是指所连接的管道直径,显然螺纹大径比公称直径大。 1/4,...

-

英制和公制的区别

英制和公制的区别,,1、计量单位不同:公制单位是以毫米为单位计算尺寸。英制单位是以英寸为单位计算尺寸。2、含义不同:英制:是英国、美国等英语国家使用的一种度量制。长度主单位为英尺,重量主单位为磅,容积主单位为加仑,温度单位为华氏度。因为各种各样的历史原因,英制的进制相当繁杂。公制:亦称“米制”、“米突制”。1858年《中法通商章程》签定后传入中国的一种国际度量衡制度。创始于法国,1795年4月7日...

-

加权分数是什么意思

加权分数是什么意思,,加权分数是指不同的比重数据的分数叫做加权分数,加权分数是将原始的数据按照合理化的的比例来计算。如果要理解加权的意思,首先就需要理解什么是“权”,“权”在古时候的含义是秤砣,就是秤上面可以通过滑动来观察质量的铁疙瘩。《孟子-梁惠王上》里面说:“权,然后知轻重”。说的就是这个意思。在加权分数里面,除去一组数据里的其中一个数字的频数称其未权重外,权重还有其他更广泛的含义。统计学里认...

-

内六角扳手英制和公制的区别

内六角扳手英制和公制的区别,,1、性质不同:公制单位是以毫米为单位计算尺寸的,英制单位是以英寸为单位计算尺寸的。2、特点不同:公制螺纹是60度等边牙型,英制螺纹是等腰55度牙型,美制螺纹60度。3、单位不同:公制螺纹用公制单位, 美英制螺纹用英制单位。 4、用途不同:管螺纹主要用来进行管道的连接,其内外螺纹的配合紧密,有直管与锥管两种。公称直径是指所连接的管道直径,显然螺纹大径比公称直径大。 1/...

-

送东阳马生序全文翻译

送东阳马生序全文翻译,,翻译我小时候特别爱好读书。家里贫穷,没有办法得到书来读,(于是)常向藏书的人家去借,亲手用笔抄写,计算着日子按期归还。(这天)天气十分寒冷,砚池里(的墨水)被冻得像冰一样硬,(而且)手指不能够自由伸屈,但却仍然不敢放松(抄书)。等到抄写完毕,跑着把书送还,不敢稍稍超过约定的期限。因为这样,许多人都愿意把书借给我,于是我虽然愚笨,终于能够有所收获。当我从师求学的时候,背着书箱...

-

送东阳马生序12段翻译

送东阳马生序12段翻译,,我年幼时就非常爱好读书。家里贫旁,无法得到书来看,常常向藏书的人家求借,亲手抄录,计算着日期按时送还。天非常寒冷,砚台里的墨汁都结了冰,手指冻得不能弯曲和伸直也不放松读书。抄写完毕后,便马上跑去还书不敢超过约定的期限。因此有很多人都愿意把书借给我于是我能够遍观群书。成年以后,我更加仰慕古代圣贤的学说,又苦于不能与学识渊博的老师和名人交往曾经赶到数百里以外,拿着经书向乡里有...

-

前方交会和后方交会

前方交会和后方交会,,前方交会:在两个已知点以上分别对待定点相互进行水平角观测,并根据已知点的坐标及观测角值计算出待定点坐标的方法。 后方交会:在待定点上向至少三个已知点进行水平角观测,并根据三个已知点的坐标及两个水平角值计算待定点坐标的方法。后方交会:空间后方交会的定义是利用地面控制点及其在像片上的像点,确定单幅影像外方位元素的方法。如果已知每张像片的6个外方位元素,就能确定被摄物体与航摄像片的...

-

未来的房子作文500字

未来的房子作文500字,,现代的房子存在着许多缺点。好像地震来临了,房子抵挡不住就会倒下,还有,如果你忘记关门,那些小偷就会小心翼翼不被你察觉的方式去你家偷东西,还有,如果房子太小,容纳不了那么多人,还有容纳不了那么多到家具该怎么办呢?......随着科学的进一步发展,科学家们终于发明了一种用纳米多材料制成的:“万能屋”,这种万能屋可以让你随便调换房子的大小,它的大门是自动门,大门里面装着一块芯片...

-

未来的书包的作文400

未来的书包的作文400,,2201年人类的科技非常发达。很多人工产品被发达的科技所取代,包括小学生的书包。那时小学生的书包与现在的书包大不相同,书包内部装有智能芯片,外面装着红黄蓝三种颜色的按钮。红色按钮可以调节书包的大小。假如你要去上学,你就可以按一下红色按钮,书包就会立刻缩小到你的手掌那么大,你可以拿着书包去上学,非常方便。可能你会问一个问题:“书包这么小,还能装下书本吗?”哈哈,你们放心吧。...

-

电脑i5是什么意思?

电脑i5是什么意思?,,1、酷睿i5处理器建基于Intel Nehalem微架构,集成了双通道DDR3存储器控制器。Core i5采用了LGA 1156。处理器核心方面,代号Lynnfiled,采用45纳米制程的Core i5会有四个核心,不支持超线程技术,总共仅提供4个线程。L2缓冲存储器方面,每一个核心拥有各自独立的256KB,并且共享一个达8MB的L3缓冲存储器。芯片组方面,采用Intel...

-

送东阳马生序安心求学的句子

送东阳马生序安心求学的句子,,1、家贫,无从致书以观,每假借于藏书之家,手自笔录(借书)。我小时侯就很爱学习。家境贫苦,不能得到书来读,每次在藏书的人家借书,亲自提笔抄录,计算着日子来归还。2、尝趋百里外,从乡之先达执经叩问(好学)。曾快步走到百里之外,手拿着经书向同乡前辈求教。3、当余之从师也,负箧曳屣,行深山巨谷中。穷冬烈风,大雪深数尺,足肤皲裂而不知。(刻苦精神)当我寻师时,背着书箱,把鞋后...

-

华为六款从中端到旗舰全覆盖哪个好

华为六款从中端到旗舰全覆盖哪个好,,预算2000多可以考虑华为畅享20 Plus,该机主打外观和快充,首先外观上采用了类似华为Mate30上的圆形相机模组,充电上则支持40W有线快充。此外华为畅享20 Plus配备天玑720处理器,内置4200mAh电池,后置4800万主摄+800万广角+200万微距三摄,1600万前摄相机。...

-

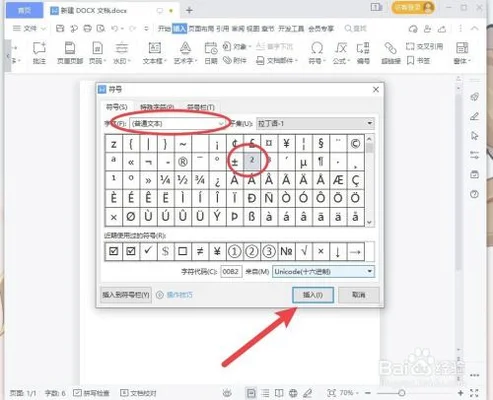

指数符号怎么打出来:?

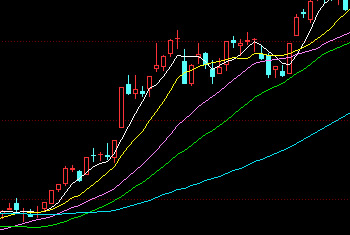

指数符号怎么打出来:?,,指数是反映股票市场整体价格水平及其变动趋势的一种相对数。它由收盘价、最高价和最低价的代数平均值组成(即:HIGHT/LOW=HI-LEVEL),以便于计算和分析。1、首先我们打开一个行情软件或者电脑自带的炒股工具——通达信证券交易客户端,然后点击【分析】—>【技术指标】。在右侧的列表中可以看到很多的技术指标,选择第一个就是【MACD】,这个是我们常用的技术分析方法之一;接...

-

更换净水器滤芯要注意什么(净水器五个滤

更换净水器滤芯要注意什么(净水器五个滤芯怎么换),,在以前的年代都知道喝水要喝干净的,但如今不同喝水要喝健康的,然而净水器就走进了家家户户,每天使用净水器非常频繁,时间长了就有人觉得净水器使出水量变的非常小,甚至直接不出水。那么更换净水器滤芯要注意什么呢?1、为了保证净水机商品能满足顾客要求,安装人员一定确保净水机进水水质,进水压力和进水量等才能满足产品性能要求。若进水水质不属于市政自来水,那必须...

-

85寸电视机什么品牌好?性价比高,值得购买

85寸电视机什么品牌好?性价比高,值得购买,,随着科技的发展和人们生活水平的提高,人们对电视机的需求也日益增长。目前市场上销售的液晶电视机主要有两种类型:LCD(Liquid Crystal Display)显示屏的平板式液晶电视、LED (Light EMitting Diode ) 显示屏的点阵式液晶电视;其中点阵型液晶显示器具有体积小重量轻功耗低显示效果好等特点而逐渐成为市场主流产品之一。1...

-

airpods pro是第几代,苹果耳机一共有几代

airpods pro是第几代,苹果耳机一共有几代?,,airpods pro的包装盒很简单正方形,便于大家携带,那airpods pro是第几代呢,让我们一起来看看吧~airpods pro是第几代airpods pro是第三代,支持主动降噪功能,可根据你耳部的几何结构和耳塞的佩戴贴合度持续进行调节,以阻隔外界噪音。在耳机芯片上,这款产品采用了苹果H1,也就是跟第二代AirPods一样,这次的H...

-

毛猪现在多少钱一斤

毛猪现在多少钱一斤,,养猪成本是指养猪的总成本,包括饲料、药品、管理费用和养殖人工费等。其中饲料占比最大,主要包括猪料中的蛋白质粉、矿物质(如食盐、骨粉或钙、磷)和维生素等。猪料成本包括直接原料(如玉米、麸皮等)约占总成本的70%,再加上饲料原料采购、加工费用等约占总成本的30%。猪饲料成本直接影响到猪的生长和生产性能,是影响养猪盈利水平的关键因素之一。猪料成本主要由原料、人工费用两部分构成。1....